Smart and Healthy Living

Stromsparende Chips für Künstliche Intelligenz

Die Fraunhofer-Institute EMFT, IIS und IPMS erforschen energieeffiziente neuromorphe Hardware.

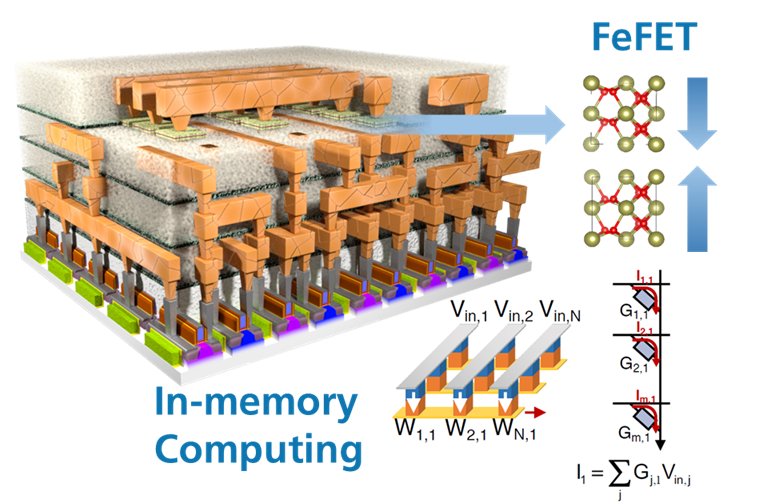

Wenn wir denken, verarbeitet unser Gehirn eine Unmenge an Informationen. Möglich macht das die Vernetzung von Milliarden von Nervenzellen durch Billiarden synaptischer Verbindungen. Neuromorphes Computing – eine Schlüsseltechnologie für Künstliche Intelligenz – ahmt diese Vernetzung nach, indem es Informationen bereits im System speichert. Das erhöht die Energieeffizenz für Anwendungen der KI, denn momentan verbraucht die komplexe Denkleistung von Rechnern noch viel Strom. Im Rahmen des ECSEL-Projekts TEMPO entwickeln die Forschenden daher neuartige und energieeffiziente neuromorphe Systeme für Halbleiterchips. Die Hardware-Architektur der Chips erlaubt die nichtflüchtige Speicherung und Verarbeitung von Informationen direkt im System. Ein komplizierter Datentransfer zwischen Prozessor und Speicher ist somit nicht notwendig. Die Forschenden setzen dabei neue integrierte Speichertechnologien in innovativen Konzepten für die Realisierung analoger und digitaler neuromorpher Schaltungen ein.

Fraunhofer-Expertise

Im Rahmen des ECSEL-Projekts TEMPO (Technologie & Hardware für neuromorphe Computersysteme) arbeiten u. a. die Fraunhofer-Einrichtung für Mikrosysteme und Festkörper-Technologien EMFT, das Fraunhofer-Institut für integrierte Schaltungen IIS und das Fraunhofer-Institut für Photonische Mikrosysteme IPMS an der Realisierung der neuromorphen Hardware.Die Fraunhofer EMFT fokussiert sich auf die Entwicklung von Schlüssel-IPs für die analoge und Mixed-Signal-Signalverarbeitung für neuromorphe Strukturen. Im Detail handelt es sich um stromsparende neuromorphe Computerchips im 22-nm-FDSOI-Technologieknoten. Gemeinsam mit dem Fraunhofer IIS ist die Fraunhofer EMFT zentraler Ansprechpartner für die Entwicklung von Schlüsselkomponenten für die analoge und Mixed-Signal neuromorphe Hardware.

Das Fraunhofer IIS wird in diesem Projekt Grundlagen für analoge Deep-Learning-Inference- Beschleuniger-Komponenten legen, die in zukünftigen IP-Core-Produkten und nachfolgenden Industrie- und Förderprojekten verwendet werden. Darauf aufbauend werden FPGA- und ASIC-basierte Mixed-Signal- Beschleuniger bestehend aus digitalen und analogen Komponenten realisiert. Der Beschleuniger wird zunächst auf FPGA implementiert und schließlich auf einen ASIC abgebildet. Das Fraunhofer IIS ist sowohl für die Koordination als auch für die Einbringung des Architekturentwurfs eines flexibel programmierbaren digitalen Deep-Learning Beschleunigers zuständig.

Das Fraunhofer IPMS arbeitet im Projekt an der Entwicklung und Evaluierung stromsparender Neuromorphic-Computing-Chips im 22-nm-FDSOI-Technologieknoten. Die Entwickler setzen dabei neue integrierte Speichertechnologien auf Basis ferroelektrischen Hafniumdioxids in innovativen Konzepten für die Realisierung analoger und digitaler neuromorpher Schaltungen ein. Dabei fokussiert sich das Fraunhofer IPMS auf die Entwicklung von Speichertechnologien und IPs für die analoge und gemischte Signalverarbeitung in den Speicherzellen, um effiziente Berechnungen zu ermöglichen.

Anwendungsfelder

Die im Projekt entworfenen und gefertigten Chips sollen vor allem für Klassifikationsaufgaben in Bilderkennungssystemen als auch für die Verarbeitung weiterer Sensordaten Einsatz finden. Die möglichen Anwendungsfelder umfassen u. a. die Bereiche Automobil, Weltraum und Gesundheit. Damit kann die Leistungsaufnahme der Signalverarbeitung mobiler und portabler Sensorsysteme um einige Größenordnungen reduziert werden.Dies minimiert den Energieverbrauch für komplexe Rechenleistungen und ermöglicht eine neuartige Computerarchitektur für Anwendungen der Künstlichen Intelligenz.

Über TEMPO:

Das Projekt wird durch die EU und durch das Bundesministerium für Bildung und Forschung (BMBF) gefördert. Weitere Informationen zum Projekt unter: www.elektronikforschung.de/projekte/tempo

Letzte Änderung: